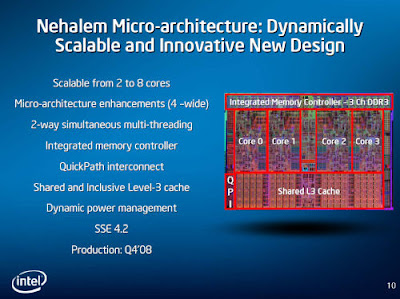

With the second phase of its 45 nm generation microprocessors -- what it calls "tock," using a metaphor that drives rival AMD mad -- Intel will move to a processor design that utilizes scalable cores, from two all the way to eight, it will introduce another new microarchitecture for processing instructions, and it will phase out the front-side bus as a component of its architecture. We've known these facts based on bits and pieces of information compiled from Intel hints over the past six months. Now we know this as absolute fact, confirmed by senior vice president Pat Gelsinger during a special presentation this morning.

Now we know when it will all happen for certain. The six-core Dunnington server CPU platform using Penryn architecture (the "tick" generation of 45 nm), with 16 MB of L3 cache, goes into production as soon as this summer. The 45 nm Nehalem architecture ("tock") enters production in the fourth quarter of this year. That will be the beginning of the end of the era of Intel x86 computers with a front-side bus (a separate circuit linking the CPU to memory, with a dedicated clock).

And Itanium lives on, as the company's new Tukwila architecture will carry the intrinsically multi-threaded instruction set into datacenters and mainframe replacements, with six cores sharing 30 MB of cache.

But it will be Nehalem that is expected to provide one very thunderous "tock." One key feature that literally creates an entirely new dimension to parallelism will be simultaneous multithreading (SMT): the ability for each core to process two threads at a time, not alternately like hyperthreading but truthfully at the same time.

An updated Nehalem white paper today (PDF available here) describes SMT as "a more energy efficient means of increasing performance for multi-threaded workloads. The next generation microarchitecture's SMT capability enables running two simultaneous threads per core -- an amazing eight simultaneous threads per quad-core processor and 16 simultaneous threads for dual-processor quad-core designs."

So a four-way quad-core Nehalem system may have to be quantified as "4 x 4 x 2," in a designation that is sure to give a new source of headaches for AMD. A few weeks ago, that company began gathering support for its first 45 nm generation, even though it won't yet feature AMD's version of the high-k-plus-metal-gate manufacturing technology it developed with IBM; that's being reserved for a future generation.

So a four-way quad-core Nehalem system may have to be quantified as "4 x 4 x 2," in a designation that is sure to give a new source of headaches for AMD. A few weeks ago, that company began gathering support for its first 45 nm generation, even though it won't yet feature AMD's version of the high-k-plus-metal-gate manufacturing technology it developed with IBM; that's being reserved for a future generation.Meanwhile, one of AMD's remaining design "edges" against Intel -- its Direct Connect memory bus -- will no longer be an edge once Intel inaugurates its QuickConnect architecture. Replacing the front-side bus will be a more direct link that Intel now calls its "QuickPath Interconnect."

"A big advantage of the Intel QuickPath Interconnect is that it is point-to-point," reads a new white paper on the subject (PDF available here). "There is no single bus that all the processors must use and contend with each other to reach memory and I/O. It also improves scalability, eliminating the competition between processors for bus bandwidth. Coupled with Intel's great cache memory, this technological achievement will enable the performance of servers and workstations to take another leap forward."

"A big advantage of the Intel QuickPath Interconnect is that it is point-to-point," reads a new white paper on the subject (PDF available here). "There is no single bus that all the processors must use and contend with each other to reach memory and I/O. It also improves scalability, eliminating the competition between processors for bus bandwidth. Coupled with Intel's great cache memory, this technological achievement will enable the performance of servers and workstations to take another leap forward."The first TPC benchmarks for the "tick" generation of Penryn architecture actually delivered a bit more performance than even independent observers were expecting. No explicit performance data or projections for Nehalem were released today, though the early word on the street is to plan not to use the word "astounding" too many times in one paragraph.

0 comments:

Post a Comment